In this note, we are going to Explain UART Communication Protocol Block Diagram. Welcome to Poly Notes Hub, a leading destination for engineering notes for diploma and degree engineering students.

Author Name: Arun Paul.

What is UART Communication Protocol?

The UART (Universal Asynchronous Receiver/Transmitter) Communication Protocol is a serial communication protocol used to transfer data between two devices. It is asynchronous, which means that the transmitter and receiver do not need a clock signal to synchronize; instead, they must agree on a common baud rate (speed).

Key features of UART Communication Protocol

- It is a asynchronous transmission (no clock signal)

- It offers full duplex communication system. (simultaneous transmit and receive)

- The communication is point to point type. (usually between two devices)

- It is very simple and cost effective as well.

- It uses only two main wires: TX (Transmit) and RX (Receive)

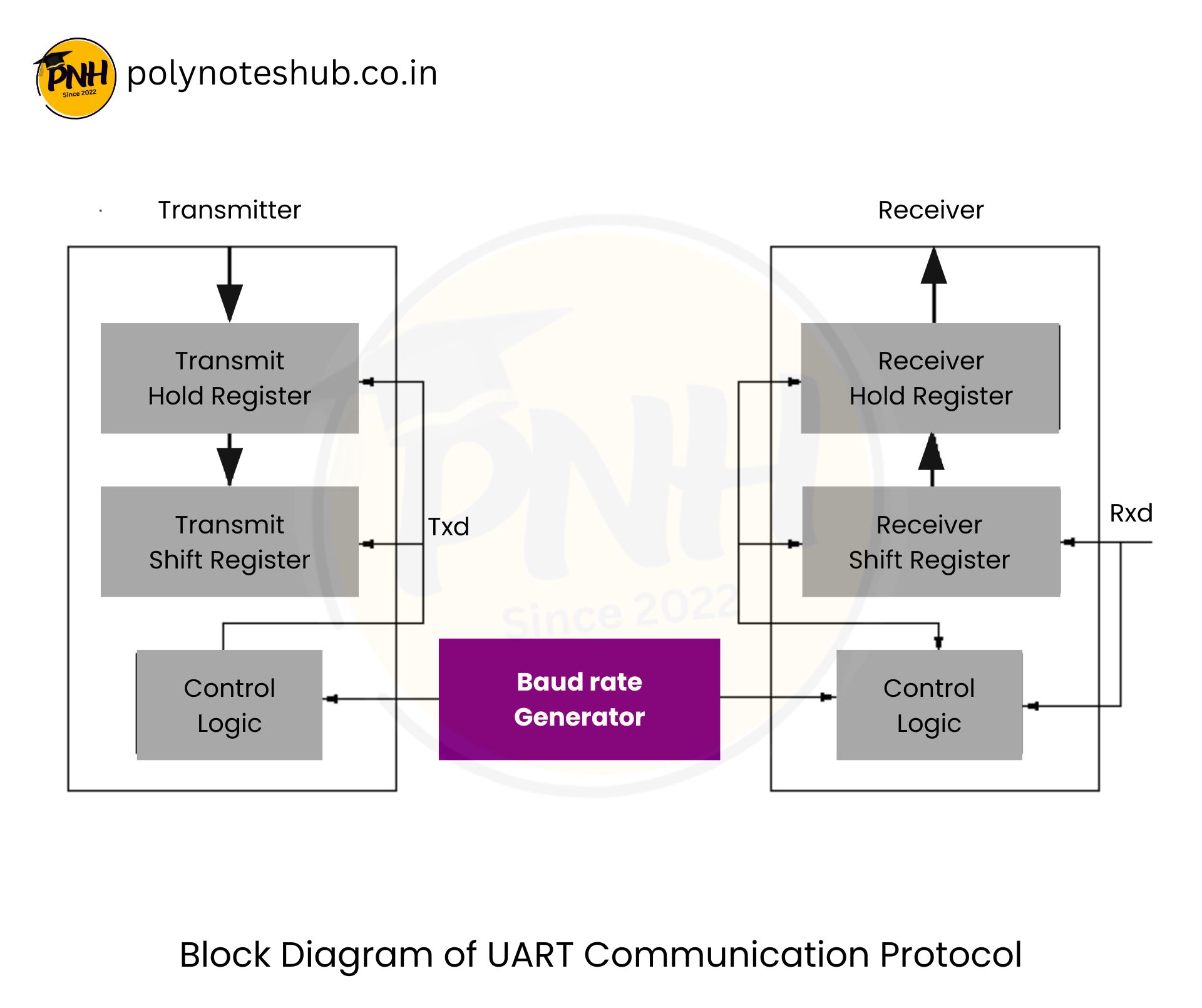

Explain UART Communication Protocol Block Diagram

1. Transmitter Side

- Transmit Hold Register: The Transmit Hold Register is responsible for temporarily storing the data that will be transferred. This data is received in parallel from the processor or memory unit. The register serves as a buffer, ensuring that the data is ready and available before proceeding to the next stage, the Transmit Shift Register. This buffering aids in smooth and uninterrupted data transmission, particularly when there is a disparity between processing and transmission speeds.

- Transmit Shift Register: The Transmit Shift Register translates the parallel data from the Transmit Hold Register into serial format. It is responsible for the important task of transferring data bit by bit to the TXD (Transmit Data) line. This register also includes the appropriate control bits, such as the start bit, optional parity bit, and stop bit(s), to properly frame the data using the UART protocol. It ensures that serial data is accurately and correctly sent to the receiver.

- Control Logic (Transmitter Side): The Control Logic unit in the transmitter part controls the flow of data between registers and organizes the entire transmission operation. It guarantees that data is transferred from the hold register to the shift register at the appropriate time, based on baud rate generator signals. This block also conducts any protocol-related actions necessary for transmission.

2. Receiver Side

- Receiver Shift Register: The Receiver Shift Register receives serial data bit by bit from the RXD (Receive Data) line. It eliminates the control bits (start, parity, and stop bits) before converting the serial data back to parallel format. This register is critical in understanding the incoming serial stream and reconstructing the original data format sent by the transmitter.

- Receiver Hold Register: The shift register converts the data into parallel format, which is briefly held in the Receiver Hold Register. This register serves as a buffer, storing the received data until the processor or memory is ready to access it. It prevents data from being lost or rewritten while it waits to be processed.

- Control Logic (Receiver Side): The data reception process is controlled by the receiver’s control logic. It handles the synchronization of incoming data, ensures proper timing, and initiates the transfer of data from the shift to the hold register. It also checks for transmission issues including parity mismatches and framing errors.

3. Baud Rate Generator

The Baud Rate Generator is a crucial component in the UART Communication Protocol system, shared by the transmitter and receiver. It generates precise timing signals to determine the rate of data transmission and reception. To ensure proper communication, both the sending and receiving UARTs must be configured with the same baud rate. The baud rate sets the number of bits delivered per second and has a direct impact on communication speed and dependability.